### **Book of Abstracts of 29th International Conference**

### MIXED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS

### **MIXDES 2022**

### Wrocław, Poland June 23 – 24, 2022

### Organised by:

Department of Microelectronics and Computer Science, Lodz University of Technology, Poland Institute of Microelectronics and Optoelectronics, Warsaw University of Technology, Poland

in co-operation with:

Poland Section IEEE - ED & CAS Chapters Section of Microelectronics & Electron Technology and Section of Signals, Electronic Circuits & Systems of the Committee of Electronics and Telecommunication of the Polish Academy of Sciences Commission of Electronics and Photonics of Polish National Committee of International Union of Radio Science – URSI

Edited by Andrzej Napieralski

Lodz University of Technology Department of Microelectronics and Computer Science ul. Wólczańska 221/223 90-924 Łódź, Poland

Phone:

+48 42 631 26 45

Fax:

+48 42 638 03 27

E-mail:

napier@dmcs.pl

Web:

http://www.mixdes.org

All rights reserved. No part of this publication may be reproduced, stored in retrieval system or transmitted in any form or by any means, electronic, electrostatic, magnetic tape, mechanical, photocopying, recording or otherwise, without prior permission in writing from the copyright owner.

Copyright © 2022 by Editor

Printed by Department of Microelectronics and Computer Science, Lodz University of Technology ul. Wólczańska 221, 93-005 Łódź, Poland

### Preface

For 28 years the MIXDES Conference is a forum devoted to recent advances in micro- and nanoelectronics design methods, modelling, simulation, testing and manufacturing technology in diverse areas including embedded systems, MEMS, sensors, actuators, power devices and biomedical applications. This year the International Conference "Mixed Design of Integrated Circuits and Systems" celebrates its 29<sup>th</sup> edition. After coronavirus (COVID-19) pandemic restrictions we can meet again in Wrocław, the capital of Lower Silesia region.

The program of the conference consists of two days of sessions starting each day with invited talks. The following invited talks will be presented:

- IC Masks The Challenges of the Newest Technologies Mariusz Niewczas (Design2Silicon Inc., USA)

- Nanoelectronic Challenges and Opportunities for Cyberphysical Systems Maria Helena Fino (Nova School of Science & Technology, Portugal)

- Ultralow Power Stretchable TFT Electronics Arokia Nathan (University of Cambridge, UK)

The program of MIXDES 2022 also includes 2 special sessions:

- Compact Modeling of Heterogeneous Devices and Systems organised by Dr. D. Tomaszewski (Łukasiewicz - Institute of Microelectronics and Photonics, Poland) and Dr. W. Grabiński (GMC, Switzerland)

- Special Session in Memory of Professor Wojciech P. Maly organised by Prof. W. Kuźmicz and Prof. A. Pfitzner (Warsaw University of Technology, Poland)

In addition to the technical sessions, the conference attendees will have an opportunity to participate in an IEEE Distinguished Lecturers' session organized by Łukasiewicz - Institute of Microelectronics and Photonics, Poland in collaboration with IEEE ED Poland Chapter.

| Country        | Number of |            | Company  | Number of |            | Country     | Number of |            |

|----------------|-----------|------------|----------|-----------|------------|-------------|-----------|------------|

|                | papers    | co-authors | Country  | papers    | co-authors | Country     | papers    | co-authors |

| Austria        | 1         | 3          | France   | 2         | 12         | Singapore   | 0         | 1          |

| Belgium        | 0         | 1          | Germany  | 3         | 17         | Slovakia    | 1         | 1          |

| Brazil         | 1         | 6          | Iran     | 0         | 1          | Spain       | 0         | 3          |

| Bulgaria       | 1         | 7          | Italy    | 1         | 2          | Sweden      | 1         | 5          |

| China          | 1         | 3          | Poland   | 27        | 67         | Switzerland | 2         | 4          |

| Czech Republic | 1         | 2          | Portugal | 3         | 2          | UK          | 2         | 2          |

|                |           |            |          |           |            | USA         | 2         | 4          |

|                |           |            |          |           |            | Total       | 49        | 143        |

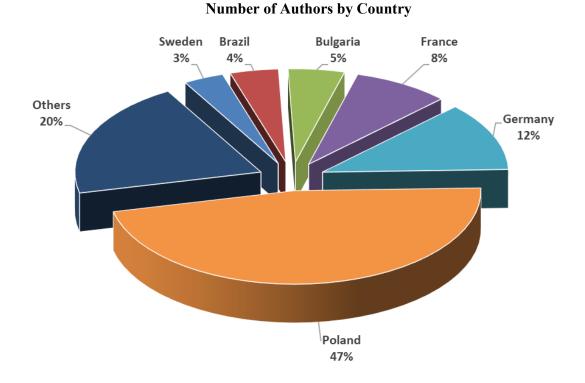

### Number of accepted papers and authors by country

All regular papers were reviewed and selected from submissions from 19 countries. The organisers would like to thank all the distinguished scientists who have supported the conference by taking part in the International Programme Committee and reviewing contributed papers.

We hope that you are safe and healthy and remain so, and we will meet together next year in Kraków, (June 29 - July 1, 2023), the most beautiful city in Poland to celebrate the  $30^{th}$  edition of the conference.

Łódź, June 2022

Andrzej NAPIERALSKI Department of Microelectronics and Computer Science Lodz University of Technology, Poland General Chairman of MIXDES 2022

### **International Programme Committee**

M. Bucher Prof J. Cabestany Prof. Prof. J. Collet A. Dabrowski Prof. G. De Mey Prof. Prof. J. Deen Prof. M.H. Fino Dr. D. Foty Prof. L. Golonka K. Górecki Prof. W. Grabiński Dr. Prof. P. Gryboś Prof. V. Hahanov Prof. A. Handkiewicz Prof. A. Hatzopoulos Prof. S. Hausman G. Jabłoński Dr. Prof. A. Kos W. Kuźmicz Prof. Prof. C. Lallement Prof. M. Lobur Dr. M.M. Louerat Prof. T. Łuba B. Macukow Prof Prof. J. Madrenas D. Makowski Dr. Prof. A. Martinez Prof. A. Materka Prof. W. Mathis J.M. Moreno Prof. Dr. M. Napieralska Prof. A. Napieralski J. Nishizawa Prof. Prof. L. Opalski Prof. A. Pfitzner Prof. E. Piętka W. Pleskacz Prof. B.F. Romanowicz Dr. Prof. J.A. Rubio Prof. A. Rybarczyk Dr. J.-M. Sallese Prof. D. Sankowski M. Schwarz Dr. Prof. T. Szmuc P. Śniatała Dr. Prof. M. Tadeusiewicz D. Tomaszewski Dr. Dr. P. Tounsi M. Turowski Dr. Prof. R. Ubar Prof. G. Wachutka K. Wawryn Prof. Prof. B. Więcek Prof. S. Yoshitomi Prof. J. Zarebski Prof.

Technical University of Crete, Greece Universitat Politecnica de Catalunva, Spain LAAS - CNRS, Toulouse, France Poznan University of Technology, Poland University of Ghent, Belgium (Vice-Chairman) McMaster University, Canada Universidade Nova de Lisboa, Portugal Gilgamesh Associates, USA Wrocław University of Science and Technology, Poland pGdynia Maritime University, Poland GMC, Switzerland AGH University of Science and Technology, Poland Kharkiv National University of Radioelectronics, Ukraine Poznan University of Technology, Poland Aristotle University of Thessaloniki, Greece Lodz University of Technology, Poland Lodz University of Technology, Poland AGH University of Science and Technology, Poland Warsaw University of Technology, Poland Strasbourg University, France State University Lviv, Ukraine Université Pierre et Marie Curie, Paris, France Warsaw University of Technology, Poland Warsaw University of Technology, Poland Universitat Politecnica de Catalunya, Spain Lodz University of Technology, Poland LAAS - CNRS, Toulouse, France (Honorary Chairman) Lodz University of Technology, Poland Leibniz University of Hannover, Germany Universitat Politecnica de Catalunya, Spain Lodz University of Technology, Poland Lodz University of Technology, Poland (General Chairman) Semiconductor Research Institute, Japan Warsaw University of Technology, Poland Warsaw University of Technology, Poland (Programme Chairman) Silesian University of Technology, Poland Warsaw University of Technology, Poland Nano Science and Technology Institute, USA Universitat Politecnica de Catalunya, Spain Poznan University of Technology, Poland Swiss Federal Institute of Technology, Switzerland Lodz University of Technology, Poland Robert Bosch GmbH, Germany AGH University of Science and Technology, Poland Poznań University of Technology, Poland Lodz University of Technology, Poland Institute of Electron Technology, Warsaw, Poland INSA de Toulouse, France Alphacore, Inc., USA Tallinn Technical University, Estonia Technische Universitaet Muenchen, Germany Technical University of Koszalin, Poland Lodz University of Technology, Poland Toshiba Corporation, Japan Gdynia Maritime University, Poland

. M. Zubert Lodz University of Technology, Poland

### **Organising Committee**

| Prof. | A. Napieralski | (Chairman)                                                                                                                   |

|-------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| Dr.   | M. Orlikowski  | (Secretary)                                                                                                                  |

| Dr.   | M. Napieralska | (Vice-Chairman)                                                                                                              |

| Dr.   | G. Jabłoński   | Department of Microelectronics and Computer Science,                                                                         |

| Prof. | W. Kuźmicz     | Lodz University of Technology, Poland<br>Institute of Micro- and Optoelectronics,<br>Warsaw University of Technology, Poland |

### **Table of Contents**

|            | Preface                                                                                                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Table of Contents   7                                                                                                                           |

| I          | General Invited Papers                                                                                                                          |

|            | IC Masks - The Challenges of the Newest Technologies                                                                                            |

|            | Nanoelectronic Challenges and Opportunities for Cyber-Physical Systems       14         M.H. Fino (Nova School of Science & Techn., Portugal)   |

|            | Ultralow Power Stretchable TFT Electronics                                                                                                      |

| <b>S</b> 1 | Special Session in Memory of Professor Wojciech P. Maly                                                                                         |

|            | Estimating and Improving IC Manufacturing Yield. Past, Present and Future                                                                       |

|            | VESTIC: A New IC Manufacturing Paradigm. Present Status and Future Plans                                                                        |

| S2         | Compact Modeling of Heterogeneous Devices and Systems                                                                                           |

|            | Advances in Qucs-S Schematic Capture for SPICE and Verilog-A Device Modelling and Circuit Simulation                                            |

|            | Compact Modeling of Channel-Resistance Effects in Reconfigurable Field-Effect Transistors                                                       |

|            | Comprehensive Design-oriented FDSOI EKV Model                                                                                                   |

|            | Impact of Mechanical Bending on the Performance of Organic Thin-Film Transistors and the Characteristic Temperature of the Density<br>of States |

|            | Multidomain Modeling for Reliability Evaluation of Devices and Microsystems Using Verilog-A                                                     |

|            | Optimization-based Determination of TFT contact Resistances in Python                                                                           |

| 1          | Design of Integrated Circuits and Microsystems                                                                                                  |

|            | 8-bit Low-Power, Low-Area SAR ADC for Biomedical Multichannel Integrated Recording System in CMOS 40nm                                          |

|            | A 50 MHz, 46 µW, 0.28% Accuracy, 67 ppm/°C Relaxation Oscillator in 40nm CMOS Process for Multichannel Integrated Biomedical Recording System   |

W. Mrzygłód, P. Kmon (AGH Univ. of Science and Techn., Poland)

| A Flexible CMOS Test-Pixel Readout System                                                                                                                                                                                                                             | . 35 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A New FPGA-based Architecture of Task Scheduler with Support of Periodic Real-Time Tasks                                                                                                                                                                              | . 36 |

| Analytical Calculation of Inference in Memristor-based Stochastic Artificial Neural Networks                                                                                                                                                                          | . 37 |

| Clock Signal Phase Alignment System for Daisy Chained Integrated Circuits                                                                                                                                                                                             | . 38 |

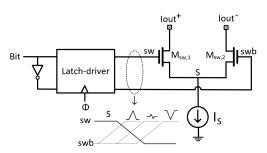

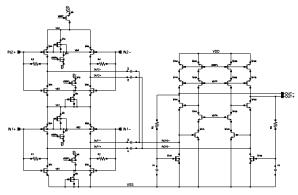

| Comparative Analysis of CMOS Latch-Driver Circuits for Current-Steering Digital-to-Analog Converters                                                                                                                                                                  | . 39 |

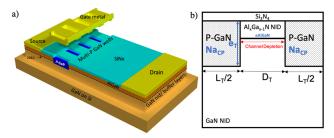

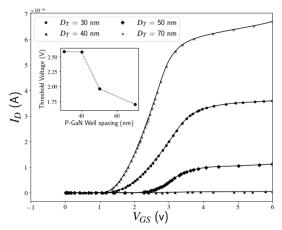

| Design Optimization of a New Nanostructured P-GaN Gate for Normally-off GaN HEMTs                                                                                                                                                                                     | . 40 |

| Design of 1.55 NEF, 2µA, Chopper Based Amplifier in 40nm CMOS for Biomedical Multichannel Integrated System                                                                                                                                                           | . 41 |

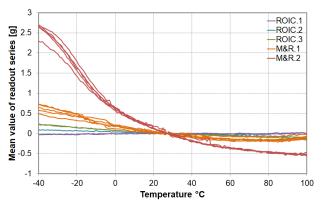

| Observation of Readout Temperature Dependence and Its Variability for the MEMS and ASIC System Specimens and Their PCB         Testbenches         M. Jankowski, J. Nazdrowicz, P. Zając, P. Amrozik, M. Szermer, C. Maj, G. Jabłoński (Lodz Univ. of Techn., Poland) | . 42 |

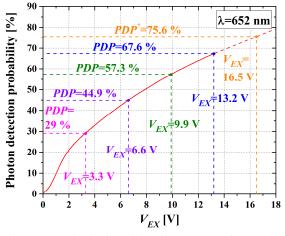

| SPAD Mixed-Quenching Circuit in 0.35-µm CMOS for Achieving a PDP of 39.2% at 854 nm                                                                                                                                                                                   | . 43 |

| Ultra Low-Power, Area-Efficient Multiplier Based on Shift-and-Add Architecture                                                                                                                                                                                        | . 44 |

### 2 Power Electronics

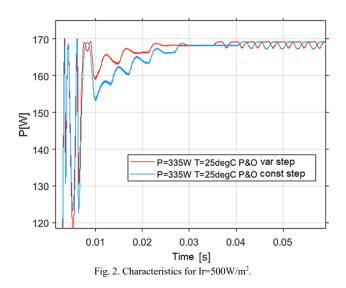

| Comparison of Photovoltaics System Response with Constant and Variable Step MPPT Algorithm                                                                                                    | 47 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| DC/DC Buck Converter Soft-Start Methods                                                                                                                                                       | 48 |

| A. Borkowski (Warsaw Univ. of Techn., Poland), K. Siwiec (Warsaw Univ. of Techn. and ChipCraft Sp. z o.o., Poland), W. Pleskacz<br>(Warsaw Univ. of Techn., Poland)                           |    |

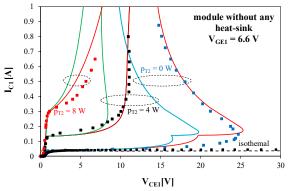

| Influence of the IGBT Module Thermal Model Form on the Accuracy of Electrothermal Computations                                                                                                | 49 |

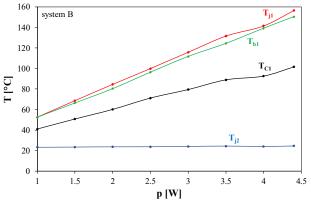

| Influence of the Measurement Method and the Cooling System on the Obtained Values of the Junction Temperature of Power MOSFETs<br>K. Górecki, K. Posobkiewicz (Gdynia Maritime Univ., Poland) | 50 |

### 3 Signal Processing

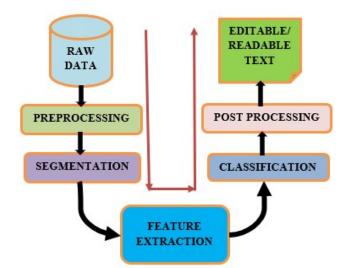

| A Comprehensive Study of Optical Character Recognition                                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

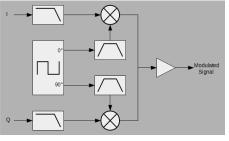

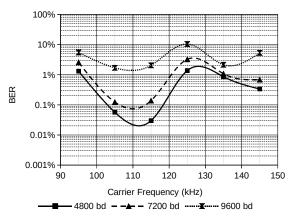

| Analog Quadrature Modulator and Coupling Circuit for Narrowband Power Line Communication                                                                                           |  |

| Data Analysis and Mining Using Logical Synthesis Methods       55         D. Wąsicki (Military Univ. of Techn., Poland), T. Łuba (Univ. of Social Sciences and Humanities, Poland) |  |

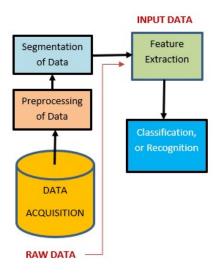

| rent Techniques for Human Activity Recognition                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

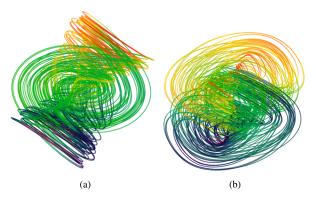

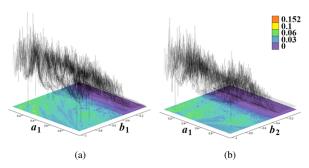

| el of Two Current-Source-Coupled Resonant Circuits with Chaotic Behavior                                                                                                                                                                                                                                                                                                                                                                                                 |

| bedded Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

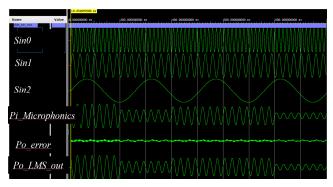

| tive Resonance Control Based on the ANC-VSS-LMS Algorithm for Microphonics Compensation                                                                                                                                                                                                                                                                                                                                                                                  |

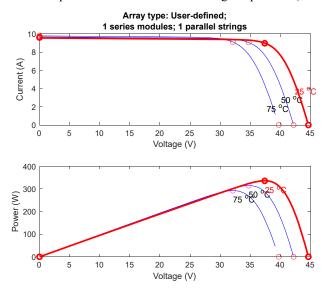

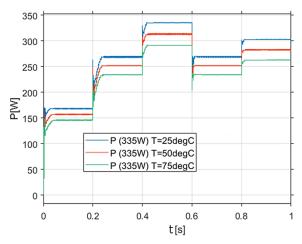

| ysis of Photovoltaics Performance Under Variable Conditions                                                                                                                                                                                                                                                                                                                                                                                                              |

| uation of Embedded Devices for Real-Time Video Lane Detection                                                                                                                                                                                                                                                                                                                                                                                                            |

| rimental Verification of the Required Power for Electrically Heated Clothing                                                                                                                                                                                                                                                                                                                                                                                             |

| vare Update for Improved Reliability Embedded Systems                                                                                                                                                                                                                                                                                                                                                                                                                    |

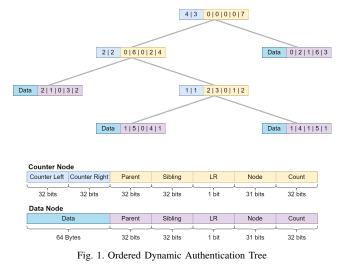

| ory Protection with Dynamic Authentication Trees                                                                                                                                                                                                                                                                                                                                                                                                                         |

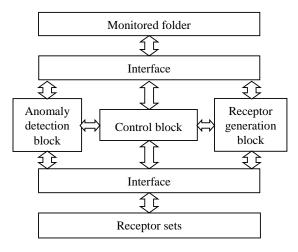

| meter Efficiency Testing for an Intrusion Detection System Inspired by the Human Immune System                                                                                                                                                                                                                                                                                                                                                                           |

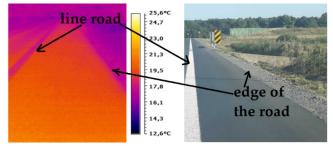

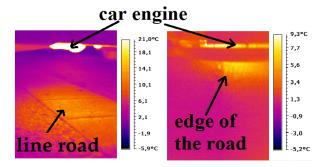

| I Line Detection by Reflected Heat                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| vare Solutions for Dynamic Configuration and Deployment of EPICS Application for MTCA.4 Chassis Management                                                                                                                                                                                                                                                                                                                                                               |

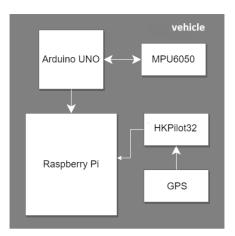

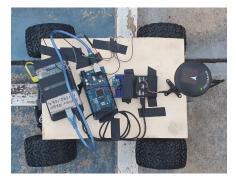

| y About Navigation Systems for Autonomous Robots                                                                                                                                                                                                                                                                                                                                                                                                                         |

| dical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| pplication of Dual-Q Tunable Q-factor Wavelet Transform for QRS Detection in ECG Signal                                                                                                                                                                                                                                                                                                                                                                                  |

| opulmoguard ICT System for Interactive Health Monitoring - Preliminary Study<br>rpiel, J. Wołoszyn, K. Olesz, M. Mysiński, M. Urzeniczok (Łukasiewicz Research Network – Institute of Medical Technology and<br>oment, Poland), M. Zieliński (Medical Univ. of Silesia, Poland), S. Głowacki (Emag-Serwis Sp. z o.o., Katowice, Poland, Poland),<br>eige, A. Sobotnicki, M. Czerw (Łukasiewicz Research Network – Institute of Medical Technology and Equipment, Poland) |

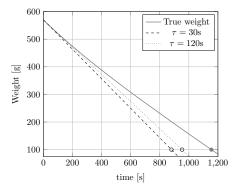

| Therapy Completion Time Assessment                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| c of Authors                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **General Invited Papers**

Book of Abstracts of the 29<sup>th</sup> International Conference "Mixed Design of Integrated Circuits and Systems" June 23-24, 2022, Wrocław, Poland

### IC Masks - The Challenges of the Newest Technologies

Mariusz Niewczas Design2Silicon Inc. 4040 Moorpark Ave suite 210, San Jose, CA, USA

Abstract—We review major problems and technical challenges related to mask making A.D. 2022. This overview is addressed to engineers dealing with physical design of ICs. Two significant advances have been just introduced to the volume manufacturing in transition from 7nm to 5nm process nodes: EUV lithography and multibeam mask writing. Combined, they improve accuracy, process margin and wafer throughput. However, they introduce various challenges and opportunities that we discuss here. Moreover, on the software side, two critical issues are being addressed currently, the data volume explosion and tremendous computational requirement. These are being addressed with the move to new data formats, curvilinear geometry and new algorithms utilizing supercomputing on GPU clusters.

*Keywords*—EUV; MultiBeam writing; Mask Data Preparartion; OPC;

### I. INTRODUCTION

The mask technology for the 5nm node and below, has become more complex and expensive. This is because two significant advances were unavoidable. The introduction of the EUV lithography scanners allowed to create smaller shapes on wafer comparing with the 193i lithography. The arrival of Multi-Beam Mask Writers (MBM) allows to write more complex masks than the Variable Size Beam (VSB) machines.

First, we will describe the construction of the EUV mask and the principles of operation of EUV scanner and MBMW. Second, we will review various topics that the mask industry deals with today: modeling of mask and lithography processes, mask inspection and repair, data volume explosion. Third, we will zoom in onto what happens between the design tape-out and writing of the mask. The process is composed of two parts: Optical Proximity Correction (OPC) [4] and Mask Data Preparation (MDP). Fourth, we will discuss the coming transition to curvilinear masks [3]. Comparing with Manhattan or octagonal shapes, it can lead to smaller layouts, better performance, and superior process window.

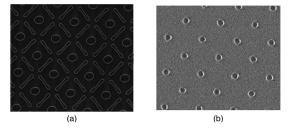

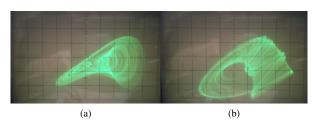

Fig. 1. (a) D2S ILT [2] curvilinear mask patterns written by the NuFlare multibeam mask writer MBM 1000 (b) the corresponding wafer prints (Source Micron)

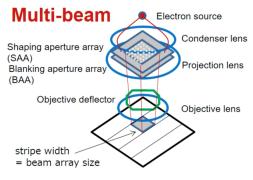

Fig. 2. The multibeam maks writer (Source: NuFlare)

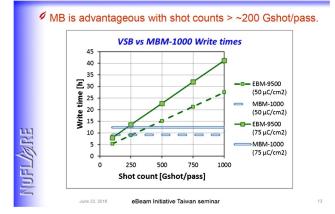

Fig. 3. Comparison of mask write time per mask shout count. For MBM-1000 the write time is theoreticvally constant so it is much fater for complex masks. (soure: NuFlafre)

- H. Zable et al., H. Zable et al. "GPU-accelerated inline linearity correction: pixel-level dose correction (PLDC) for the MBM-1000", "GPU-accelerated inline linearity correction: pixel-level dose correction (PLDC) for the MBM-1000,"

- [2] L. Pang et al., "Breakthrough curvilinear ILT enabled by multi-beam mask writing," *Journal of Micro/Nanopatterning, Materials, and Metrology* 20(4), 041405 (17 November 2021)

- [3] Mark Lepedus, "The Quest For Curvilinear Photomasks", Semiconductor Engineering, Apr. 15, 2021, https://semiengineering.com/the-quest-forcurvilinear-photomasks/

- [4] L. Pang, "Inverse lithography technology: 30 years from concept to practical, full-chip reality", J. of Micro/Nanopatterning, Materials, and Metrology, 20(3), 030901 (2021). https://doi.org/10.1117/1.JMM.20.3.0309

### Nanoelectronic Challenges and Opportunities for Cyber-Physical Systems

Maria Helena Fino Department of Electrotechnical and Computer Engineering Nova School of Science and Technology CTS - Center of Technology and Systems - UNINOVA Caparica, Portugal hfino@fct.unl.pt

Abstract—Over the last decades nanoelectronics have face an unprecedent evolution. Not only have the so-called conventional devices faced the development of new Mosfet device structures enabling the implementation of ever smaller device sizes operating at higher frequencies, but new unconventional devices have emerged as well. Also, the possibility of integrating intelligent nano sensors and actuators yields the possibility to modify our everyday life through cyber-physical systems. On the other hand, the application of these cyber-physical systems to a wide range of application domains, is also fueling the development of new devices with ever demanding specifications. This paper deals with the opportunities and challenges for nanoelectronics in their application in Cyber-physical systems

*Keywords*—Nanoelcetronics, compact modeling, prameter extraction, VerilogA, Cyber-Physical Systems

#### I. INTRODUCTION

During the last decades the evolution of nanotechnologies has yielded the development of advanced components enabling the implementation of electronic equipment with increased capabilities, better performance, lower power consumption, and smaller form factors. Applications have moved from being stationary to becoming portable and wearable by people. More recently, the possibility for designing intelligent nano actuators/ sensors that can be integrated in communicating objects, capable of generating, exchange, and consume data with minimum human intervention, has made possible the "Internet of Things." More recently the evolution of nano technology has made possible the birth of Cyber-Physical (CPs) systems involving other physical objects such as wearable devices, vehicles, homes, buildings, and even energy systems, in which continuous sensing and computing takes place[1].

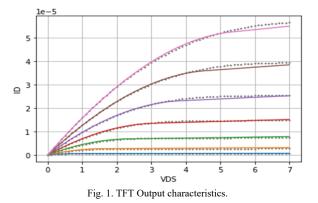

The innovation and development of CPs relies on the input of many disciplines, and Nano Electronics is expected to be a key enabling technology (KET) to sustain the development of future smart sensing systems and/or Cyber-Physical Systems. In this paper the challenges for nanolectronics arising from the increased domains of application of CPs is addressed. Starting from an overview of nanoelectronics evolution, from conventional MOSFET transistors, different MOSFET structures for CMOS devices till what is usually referred to as non-conventional Nano devices, the need for developing advanced modelling techniques at different abstraction levels is pointed out. For the different levels, challenges for the development of the models are identified. In particular, the automatic evaluation of model parameters given data resulting from measurement of devices characteristics, is analysed and a working example considering the automatic determination of TFT model parameters is illustrated[2]. The high accuracy of results obtained is demonstrated by comparing the output characteristics of a TFT with W/L=50/20 [µm] obtained with the model, against those obtained from measurements (in doted), as illustrated in Fig. 1. Finally, the specificity of using VerilogA in the development of device models to be integrated into electrical simulators is considered. The case for a nonconventional device, i.e. a memristor, model is presented, and results illustrating the transient simulation in spectre of the device in both soft and hard regimes are presented.

- M. Bhrugubanda, "A Review on Applications of Cyber Physical Systems," *IJISET-International J. Innov. Sci. Eng. Technol.*, vol. 2, no. 6, pp. 728– 730, 2015, [Online]. Available: www.ijiset.com.

- [2] M. H. Fino and P. Barquinha, "A Model-oriented Methodology for the Automatic Parameter Extraction of TFT Model. BT - 2021 28th International Conference on Mixed Design of Integrated Circuits and System, Lodz, Poland, June 24-26, 2021." pp. 27–30, 2021, doi: 10.23919/MIXDES52406.2021.9497605.

This work is funded in part by the Portuguese "Fundação para a Ciência e a Tecnologia" (FCT) in the context of the Center of Technology and Systems CTS/UNINOVA/FCT/NOVA, reference UIDB/00066/2020"

### Ultralow Power Stretchable TFT Electronics

Arokia Nathan<sup>1</sup>, Chen Jiang<sup>2</sup>, Jun Yu<sup>3</sup>, Hanbin Ma<sup>4</sup>

<sup>1</sup>Darwin College, University of Cambridge, Cambridge, UK

<sup>2</sup>Department of Electronic Engineering, Tsinghua University, Beijing, China <sup>3</sup>School of Information Science and Engineering, Shandong University, Qingdao, China

<sup>4</sup>SIBET, Chinese Academy of Sciences, Suzhou, China

# Abstract—This paper reviews design considerations of flexiblethin-film transistors and sensor interface circuits operating in thedeep sub-threshold regime for ultralow power consumption. Thedevices and circuits are layered on fiber, and by using strip-helix-fiber coiling architecture, high extrinsic stretchability is achievedwithout causing electrical performance degradation.

*Keywords*—organic thin film transistor; stretchable electroncs; deep-subthreshold operation; ultralow power

### I. INTRODUCTION

Advances in low temperature, large area, and low cost process integration technologies hold great promise for thin film transistor (TFT) electronics for a new generation of applications beyond displays. In particular, there is growing interest for realisation of wearable devices that can monitor the physiological state of the human in real time, for continuous healthcare monitoring [1,2]. For TFT electronics to be deployed in wearable devices as sensor interfaces and signal processors, new circuit architectures for high stretchability and ultralow power operation are needed. Ultralow voltage/current operation is especially important so as to achieve a high resolution of the sensory signal. This talk will review current state-of-the-art in thin film electronics, and demonstrate examples of TFT operation for sensor interfacing, along with circuit-system architectures for high stretchability. The approaches considered are fully-compatible with display processes. A new concept for an integrated, highly stretchable system will be demonstrated based on a strip-helix-fiber coiling architecture.

#### II. DEVICE FABRICATION

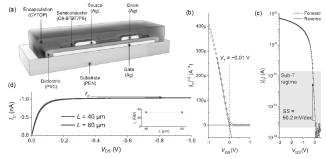

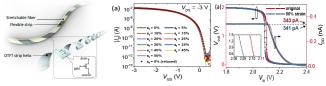

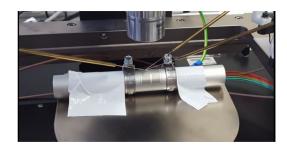

The OTFT devices and circuits presented here were layered on strip fibre using an all-ink-jet-printing process. Using a FUJIFILM DIMATIX inkjet printer, silver ink was printed to form electrode contacts, polyvinyl cinnamate (PVC) crosslinked by UV for the dielectric, C8-BTBT blended with polystrene for the semiconductor, and CYTOP as the encapsulation (Fig.1). The substrates used were trimmed polyethylene naphthalate (PEN) Teonex strips of 1mm width and 25µm thickness. To enable high extrinsic stretchability without compromising the TFT's electrical performance, a strip-helix-fiber coiling architecture was used (Fig.2), whereby the strip was wrapped around by a 875-µm-radius polyurethane (PU) core carrier-fiber. This provided strain compensation of the coiled helix by allowing change in the coiling angle. The inkjet-printed TFTs and circuits operate in deep-subthreshold providing the crucial benefit of ultralow power and high gain [3,4], with stretchability attributes that allow the circuits to be weaved or knitted into smart textiles/fabrics.

### III. RESULTS AND DISCUSSION

The devices and circuits were characterization using the Keithley 4200 Semiconductor Parameter Analyzer. The characteristics shown in Fig.1 were measured with test OTFTs printed on a glass substrate. The devices yield a low threshold voltage and a steep sub-threshold slope by virtue of low interface state density at the semiconductor-dielectric interface. Stretchability tests were carried out with the strip helix OTFT coiled around a stretchable PU fiber at a helix angle of 59° to allow for precise control of the strain during electrical measurements. The transfer characteristics shown in Fig.2 are for a carrier-fiber strain varying from 0 to 50%, as well as after it was relaxed to its original state. No changes were observed in the electrical characteristics.

Fig. 1. Device cross-section of printed OTFT and its current-voltage and transfer characteristics on linear and log scales.

Fig. 2. Schematic illustrating the OTFT strip helix coiled around a stretchable fiber. Transfer characteristics of the strip-helix-fiber OTFT under different strains. Output voltage ( $V_{out}$ ) and operating current ( $I_{DD}$ ), under relaxed and 50% strain conditions.

- A. Nathan et al., "Flexible Electronics: the next ubiquitous platform," Proc IEEE 100 (Special Centennial Issue), 1486-1517, 2012.

- [2] C. Jiang, C. P. Tsangarides, X. Cheng, L. Ding, H. Ma and A. Nathan, "High Stretchability Ultralow-Power All-Printed Thin Film Transistor Amplifier on Strip-Helix-Fiber," 2021 IEEE International Electron Devices Meeting (IEDM), 2021, pp. 16.4.1-16.4.4.

- [3] C. Jiang, H.W. Choi, X. Cheng, H. Ma, D.G. Hasko, A. Nathan, "Printed subthreshold organic transistors operating at high gain and ultralow power," Science, vol. 363, 719-723, 2019.

- [4] C. Jiang, X. Cheng, A. Nathan, "Flexible ultralow-power sensor interfaces for e-skin," Proc. IEEE, vol. 107, 2084-2105, 2019.

## Special Session in Memory of Professor Wojciech P. Maly

### **Professor Wojciech Paweł MAŁY**

January 5, 1946 - December 20, 2021

an outstanding academic teacher of Warsaw University of Technology and Carnegie Mellon University in Pittsburgh, a world-class scientist in the field of microelectronics

For almost half a century he was associated with the Institute of Microelectronics and Optoelectronics (IMiO) at Warsaw University of Technology, and simultaneously for about 35 years with Carnegie Mellon University in Pittsburgh, where he worked at the Department of Electrical and Computer Engineering as the Whitaker Chair Professor, and as co-director of the SEMATECH Center of Excellence CMU.

Professor Mały was a pioneer in the field of design for manufacturability. He created the concept of statistical simulation of microelectronic manufacturing processes, many new ideas for design and test of circuits, in conjunction with the analysis of economics of integrated systems production. His best-known works concerned the disturbances of manufacturing processes in microelectronics: the influence of random disturbances of process parameters, dependence of production yield on defects, yield optimization, testing of systems in terms of the observability of defects. His work, however, covered a much wider area. He dealt with, among others, automation of integrated circuit layout design, foresaw the development paths of microelectronics towards large-scale systems (wafer scale integration), 2.5D and 3D systems. For several years he had been working on the innovative technology of VESTIC integrated circuits (Vertical-Slit Transistor based Integrated Circuits), he was the author of.

Publication achievements of Prof. Mały are impressive: ground-breaking articles in the most prestigious magazines, invited plenary papers at the most important conferences, as well as patents and books. His outstanding achievements were recognized by invitations to program and steering committees of many top-level symposia and conferences and invitations to editorial committees of IEEE and other journals.

Prof. Mały was honored with many awards and prizes. He received awards of the Rector of the Warsaw University of Technology and the award of the Ministry of Higher Education for research achievements, the Technical Excellence Award granted by Semiconductor Research Corporation. He received a Fellowship from the Deutsche Forschungsgemeinschaft and was also elected an IEEE Fellow and a member of the IEEE Awards Board Committee, IEEE Circuit and System Society Representative in IEEE Solid State Council, IEEE Circuit and System Society VLSI Committee.

Prof. Mały, as internationally recognized expert, was appointed as an advisor and consultant to a number of leading research laboratories, both at universities and leading microelectronic companies. In particular, he cooperated with the Technical University of Munich, Technical University of Eindhoven, Fraunhofer Gesellschaft, Siemens Corporate Research and Development, VLSI Research Lab. National Semiconductor, NPCP Warsaw, Fairchild Research Lab. He was an advisor to Philips Semiconductor R&D in Nijmegen, consultant for National Semiconductor, Knights Technology, Inc. (Palo Alto CA). He was the member of the Advisory Board of Advantest Inc., Cadence Design System and chaired the Advisory Board of PDF Solutions, Inc.

Prof. Mały was an outstanding academic teacher, tutor of several generations of electronics engineers and scientific staff. His lectures, projects and care for graduate and doctoral students were recognized by numerous awards, such as the prestigious Aristotle Award from Semiconductor Research Corporation in recognition of pioneering teaching methods and ground-breaking research in the semiconductor industry.

In the opinion of students and colleagues, the contribution of Professor Wojciech Mały to the development of semiconductor technology and the impact he had as a teacher and mentor of many people in the microelectronics community cannot be overestimated. His vision and ideas are part of the essence of this field today.

With deep sorrow we said goodbye to the Great Scientist and to a Friend of many of us. This session is dedicated to his memory.

### Estimating and Improving IC Manufacturing Yield Past, Present and Future

Wieslaw Kuzmicz

Institute of Microelectronics and Optoelectronics Warsaw University of Technology Warsaw, Poland wieslaw.kuzmicz@pw.edu.pl

*Abstract*—IC manufacturing yield has been the crucial technical and economical issue since the beginning of the microelectronic industry. This presentation gives an overview of the methods and tools helping to estimate and improve yield, including current challenging problems.

*Keywords*—manufactiring yield; process variability; spot defects; statistica process simulation; critical area

#### I. INTRODUCTION

In the first years of IC manufacturing "trial and error" was the only design methodology, supported by an early version of Spice, the only available EDA tool. Although many ICs have been successfully fabricated, yield was unpredictable, and it was unclear what to do to improve it. Two main "yield killers" are: variability of the components' parameters (leading to unacceptable spread of circuit parameters) and spot defects (causing shorts and opens and resulting in nonfunctional circuits). Methodologies and EDA tools intended to understand and mitigate them appeared [1-4]. Research in the area later named "Design for Manufacturability" started and later was combined with economic considerations [6]. With rapid increase of complexity of manufacturing technologies and size of VLSI circuits early versions of EDA tools soon became obsolete or even unusable. New methodologies and tools were needed. This presentation shows the evolution of these methodologies and tools starting from the era of "10 mm feature size" ICs up to sub-10 nanometer VLSI circuits.

#### II. VARIABILITY

Well known and still routinely used methodology to estimate variability effects on IC performance and yield are: circuit simulation at process corners and statistical Monte Carlo circuit simulation. Simulation at process corners often overestimates variability effects and leads to overdesign. Monte Carlo simulation gives more realistic results if local and global variations are correctly accounted for. However, link to manufacturing process is missing. The statistical data needed to carry out such simulations come from experiment. The idea of statistical Monte Carlo simulation of manufacturing process [1] was introduced in 1982 and later extended and improved by adding link to layout. Unfortunately, it turned out that this kind of EDA tools is impractical for two reasons: (1) state-of-the-art processes are too complex to allow realistic statistical simulation in reasonable time, and (2) process settings are treated as strictly confidential, not available to circuit designers. TCAD tools for numerical process simulation do exits, but they are used for process development, and are not applicable to circuit design.

#### III. SPOT DEFECTS

A key link between circuit layout and density of spot defects is the concept of critical area [2,3]. It allows to estimate yield limited by spot defects. It can also be used to find layout areas that can be improved to reduce sensitivity to spot defects, and to determine some of the DRC rules. Critical area-inspired considerations were also used to propose methods of generating better test sequences for digital circuits [5,7]. However, critical area estimations for large layouts with millions of transistors is computationally expensive. Moreover, critical area concept is less applicable to deep submicron and nanometer ICs, which require OPC, multiple patterning etc. to avoid unacceptable layout distortions.

### IV. CURRENT CHALLENGES

New device structures (FDSOI, FinFET, GAA) and EUV lithography make yield estimation even more difficult. Many more physical factors increase variability and affect yield. New EDA tools, such as e.g. photolithography simulators, improve yield by reducing process-related variability, reducing of distortion of layout shapes etc. These tools are for manufacturers, not for circuit designers. The "good old" simple methodologies (simulation at process corners, Monte Carlo simulation) are still in use. Post-layout circuit extraction and Monte Carlo simulation can provide fairly realistic picture of variability of circuit parameters and help to reduce it.

- W. Maly and A. J. Strojwas, "Statistical Simulation of the IC Manufacturing Process," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 1, no. 3, pp. 120-131, July 1982, doi: 10.1109/TCAD.1982.1270003.

- [2] W Maly and J. Deszczka, "Yield estimation model for VLSI artwork evaluation," in *Electronics Letters*, vol. 9, no. 6, pp. 226-227, March 1983.

- [3] W. Maly, "Modeling of Lithography Related Yield Losses for CAD of VLSI Circuits," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 4, no. 3, pp. 166-177, July 1985, doi: 10.1109/TCAD.1985.1270112.

- [4] W. Maly, "Computer-aided design for VLSI circuit manufacturability," in *Proceedings of the IEEE*, vol. 78, no. 2, pp. 356-392, Feb. 1990, doi: 10.1109/5.52217.

- [5] J. P. Shen, W. Maly and F. J. Ferguson, "Inductive Fault Analysis of MOS Integrated Circuits," in *IEEE Design & Test of Computers*, vol. 2, no. 6, pp. 13-26, Dec. 1985, doi: 10.1109/MDT.1985.294793.

- [6] W. Maly, "Cost of Silicon Viewed from VLSI Design Perspective," 31st Design Automation Conference, 1994, pp. 135-142, doi: 10.1145/196244.196311.

- [7] M. Blyzniuk, I. Kazymyra, W. Kuzmicz, W. A. Pleskacz, J. Raik and R. Ubar, "Probabilistic analysis of CMOS physical defects in VLSI circuits for test coverage improvement", in *Microelectronics Reliability*, vol. 41, no. 12, pp. 2023-2040, December 2001, doi: 10.1016/S0026-2714(01)00092-0.

This paper is dedicated to the memory of Professor Wojciech Mały.

### **VESTIC:** A New IC Manufacturing Paradigm

Present Status and Future Plans

Andrzej Pfitzner Institute of Microelectronics and Optoelectronics Warsaw University of Technology Warsaw, Poland andrzej.pfitzner@pw.edu.pl

Abstract—The VESTIC (Vertical-Slit Transistor based Integrated Circuit) technology is an innovative way to implement very large-scale nanoelectronic integrated systems. The simulation and experimental feasibility studies performed so far indicate that this novel paradigm is an extremely attractive alternative to the existing most advanced technologies based on the structure of the MOS transistor

*Keywords* — VESTIC, Vertical-Slit Transistor based Integrated Circuit, VeSFET, Vertical-Slit Field-Effect Transistor, junction-less transistor, twin-gate transistor, regular layout, dynamic reconfiguration

#### SUMMARY

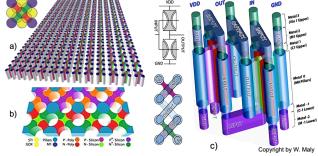

The key concept of VESTIC, proposed by W. Mały [1, 2, 3], is the original, three-dimensional architecture of active elements, ensuring full regularity of the circuit topography and defining the structure of transistors by simple shapes based on circles (Fig. 1). The electrical contacts are vertical, evenly spaced columns that constitute the canvas of the system and, at the same time, the passages through the silicon layer (via) between the upper and lower layers of electrical connections, thus enabling vertical communication for electrical signals and creating an efficient heat distribution network.

Fig. 1. VESTIC architecture: a) standard and b) densiest matrix of elements, c) inverter - electrical connections above and below the silicon layer.

The VESTIC technology has the potential to achieve ultra large scale of system integration with reduced implementation and production costs of new products due to: regularity of the system topography, reduction of the area occupied by individual transistors (scaling even beyond 7-nm node [8]), improved heat dissipation, full 3D integration possible and integration of various types of transistors (both field and bipolar) while maintaining the layout regularity.

This article is dedicated to the memory of Professor Wojciech Mały.

Further benefits arise from the use of the new junction-less transistor: VeSFET (Vertical-Slit Field-Effect Transistor) as a base component (Fig. 2).

Fig. 2. VeSFET structure: 3D geometry and top view.

The attractive electrical properties of VeSFETs (such as very slight leakage currents, excellent ratio of the on-to-off current, almost perfect subthreshold characteristic) predicted on the basis of physical analyses [2, 4], were confirmed by measurements of test structures performed at IMO A\*STAR Singapore [3, 6], EPFL Lausanne [5] and ITE Warsaw [7].

The VeSFET has two electrically symmetrical independently biased gates, which enables the effective control of its properties, a dynamic reconfiguration of the system functionality [9] and designing logic gates with a reduced number of elements. Moreover, a simpler structure and a different principle of operation make it possible to further reduce of production costs of circuits composed of VeSFETs in comparison with modern CMOS technologies.

Future plans for feasibility studies and production of innovative systems in VESTIC technology for various applications will mainly focus on low-power and reconfigurable circuits as well as sensors and non-volatile memories using 3D integration.

- W. Maly, U.S Patent 2009/0321830, Dec. 31, 2009 (Patent Appl. WO 2007/133775 A2, 2007).

- [2] W. Maly, A. Pfitzner, CMU, Techreport No. CSSI 08-02, Jan. 2008.

- [3] W. Maly, et al., Proc. 18th Int. Conf. MIXDES, 2011, pp. 145–150.

- [4] A. Pfitzner, Proc. 18th Int. Conf. MIXDES, 2011, pp. 151–156.

- [5] L. Barbut et al., Int. Semiconductor Conf. (CAS), 2011, pp. 325–328.

- [6] A. Kamath et al., IEEE Electron Device Letters, 2012, pp. 152 154.

- [7] D. Tomaszewski et al., EUROSOI Workshop and ULIS, Athens 2017.

- [8] P-L. Yang et al., IEEE Trans. on Electron Dev., 2016, pp. 3327 3334.

- [9] P-L. Yang, M. Marek-Sadowska, IEEE Trans. on VLSI Systems, 2018, pp. 1209 – 1222.

# Compact Modeling of Heterogeneous Devices and Systems

### Advances in Qucs-S Schematic Capture for SPICE and Verilog-A Device Modelling and Circuit Simulation

Mike Brinson Centre for Communications Technology London Metropolitan University UK email: mbrin72043@yahoo.co.uk Daniel Tomaszewski Łukasiewicz - Institute of Microelectronics and Photonics Warsaw, Poland e-mail: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### EXTENDED ABSTRACT

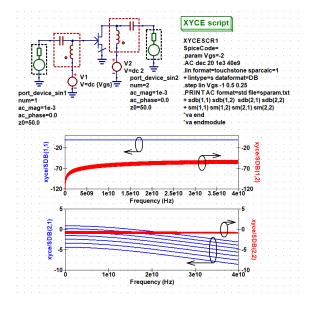

This paper introduces a schematic capture technique for generating and extracting two or more hardware description language (HDL) netlists or code modules from a single circuit diagram or device model drawing. Conventional schematic capture acts as a circuit simulator front-end for drawing circuit or device model diagrams on a high resolution computer graphics workstation. Output is normally a text file listing component types, values, and connections plus commands to control the circuit simulation process. The de facto industrial netlist format for circuit simulation is based on Berkeley SPICE. The current generation of FOSS (Free Open Source Software) circuit simulators, either derived from SPICE, for example Ngspice [1], or developed separately, for example Xyce [2], have adopted the de facto SPICE netlist format with additional simulation commands and device models. Due to the growing complexity of semiconductor compact device models there has in recent years been a move from compact model coding in C or C++ to Verilog-A HDL [3]. In parallel to semiconductor device modeling with Verilog-A the long established techniques of model construction using behavioural modeling or macromodeling [4] are still popular and significant. The nature of SPICE behavioural modeling allows device models and circuits to be constructed in stages and tested using simulation "on-the-fly". However, on successful completion and testing of a model the translation of its netlist to a Verilog-A module code has normally to be done manually. This can be both complex and error prone. The simulation front-end technique reported here introduces a new approach to schematic capture where one, or more, HDL are combined with behavioural SPICE modeling. This paper outlines the details of a new schematic capture process that has been implemented with the Qucs-S/Xyce simulator [5]. To demonstrate the application of the advances in schematic capture, particularly in compact device modeling, the construction of a GaAs MESFET TriQuint Own Model (TOM3) [6] [7] is presented. Fig.1 illustrates a typical TOM3 S-parameter two port test bench and simulation data.

Fig. 1. N-channel TOM3 MESFET S-parameter two port test bench and simulation plots: SdB(1,1), SdB(1,2), SdB(2,1) and SdB(2,2) against frequency.

- Ngspice mixed-level/mixed-signal circuit simulator based on Berkeley SPICE 3f5. Ngspice project team. Version ngspice-36. [Accessed March 2022] [Online] Available http://www.ngspice.sourceforge.net.

- [2] Xyce parallel electronic circuit simulator. Sandia National Laboratories. Version 7.4. [Accessed March 2022] [Online] Available https://xyce.sandia.gov/.

- [3] Accellera, Verilog-AMS Language Reference Manual. Version 2.2. [Accessed March 2022] [Online] Available http://www.accellera.org,

[4] J.A.Connelly and Pyung Choi, "Macromodeling with SPICE". Englewood

- [4] J.A.Connelly and Pyung Choi, "Macromodeling with SPICE". Englewood Ciffs, New Jersey:Prentice Hall. 1992.

- [5] V. Kusnetsov and M. Brinson, "Ques-S: Ques with SPICE". Version 0.0.22. [Accessed March 2022] [Online] Available https://ra3xdh.github.io/.

- [6] R.B Hallgren and D.S Smith, "TOM3 Equations" Triquint Internal Report (unnumbered), 2 December 1999.

- [7] R.B. Hallgren and P.H. litzenberg. "TOM3 Capacitance Model Linking Large- and Small-signal MESFET Models on SPICE." IEEE Trans. Microwave Theory Tech., vol. 47, no. 5. pp. 556-561, 1999.

### Compact Modeling of Channel-Resistance Effects in Reconfigurable Field-Effect Transistors

Christian Roemer<sup>1,2</sup>, Ghader Darbandy<sup>1</sup>, Mike Schwarz<sup>1</sup>, Jens Trommer<sup>3</sup>, Maik Simon<sup>3,4</sup>, André Heinzig<sup>4,5</sup>,

Thomas Mikolajick<sup>3,4,5</sup>, Walter M. Weber<sup>6</sup>, Benjamín Iñíguez<sup>7</sup>, Alexander Kloes<sup>1</sup>

<sup>1</sup> NanoP, TH Mittelhessen - University of Applied Sciences, Giessen, Germany

<sup>2</sup> DEEEA, Universitat Rovira i Virgili, Tarragona, Spain

<sup>3</sup> NaMLab gGmbH, Dresden, Germany

<sup>4</sup> Center for Advancing Electronics Dresden (cfaed), TU Dresden, Dresden, Germany

<sup>5</sup> Chair for Nanoelectronics, TU Dresden, Dresden

<sup>6</sup> Institute of Solid State Electronics, TU Wien, Vienna, Austria

<sup>7</sup> DEEEA, Universitat Rovira i Virgili, Tarragona, Spain

e-mails: christian.roemer@ei.thm.de

### EXTENDED ABSTRACT

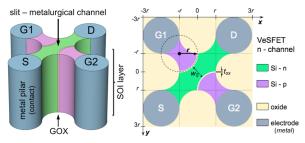

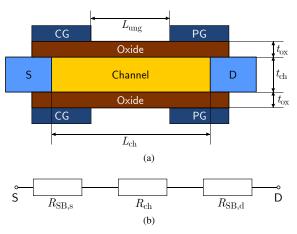

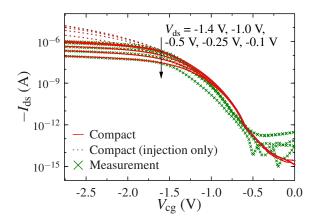

In [1] we introduced a compact model that is applicable on reconfigurable field-effect transistor (RFET) and calculates the injection currents over the Schottky barriers of these devices. Unlike standard metal oxide semiconductor fieldeffect transistors (MOSFETs), the RFET has two independently controllable gates [2]. The control gate (CG) is used to control the current flow through the device as in regular MOSFET application, while the program gate (PG) is used to determine the device's polarity [2]. A cross section of an RFET is shown in Fig. 1. For devices with long channel lengths (up to a few micrometers) or with longer gate-to-gate distances  $(L_{ung})$  the current blocking mechanism of its channel (demonstrated as  $R_{ch}$  in Fig. 1b) becomes more dominant compared to the Schottky barrier injection of the source and drain side (demonstrated as  $R_{\rm SB,s}$  and  $R_{\rm SB,d}$  in Fig. 1b), leading to deviations in the injection model from [1] for some bias conditions (demonstrated in Fig. 2 as brown dotted lines).

In this work we present a closed-form and physics-based compact model that combines the injection-based current calculation from [1] with a MOSFET model that represents the channel resistance ( $R_{\rm ch}$  of Fig. 1b) of such devices, in order to obtain the total device current. The results are demonstrated in Fig. 2 as solid red lines compared to measurements from [3] (green markers). It shows a good agreement between model and measurements and demonstrates the functionality of the model addition presented in this work.

#### References

- C. Roemer, G. Darbandy, M. Schwarz, J. Trommer, A. Heinzig, T. Mikolajick, W. M. Weber, B. Iniguez, and A. Kloes, "Physics-based DC compact modeling of schottky barrier and reconfigurable field-effect transistors," *IEEE Journal of the Electron Devices Society*, pp. 1–1, 2021.

- [2] A. Heinzig, S. Slesazeck, F. Kreupl, T. Mikolajick, and W. M. Weber, "Reconfigurable silicon nanowire transistors," *Nano Letters*, vol. 12, no. 1, pp. 119–124, Dec. 2011.

- [3] M. Simon, B. Liang, D. Fischer, M. Knaut, A. Tahn, T. Mikolajick, and W. M. Weber, "Top-down fabricated reconfigurable FET with two symmetric and high-current on-states," *IEEE Electron Device Letters*, vol. 41, no. 7, pp. 1110–1113, Jul. 2020.

Fig. 1. (a) Schematic cross-section of an RFET showing the relevant geometric parameters for the compact model. (b) Simplified equivalent circuit, showing the resistances of the source and drain side Schottky barriers, as well as the resistance of the (ungated) channel, that carriers have to pass.

Fig. 2. P-type transfer characteristics calculated from the compact model (red) compared to measurements from [3] (green) and to the injection-based compact model model results of [1] (brown dotted lines). During the transfer characteristics measurement the PG was fixed to  $V_{\rm pg} = -2.8$  V. The device has a channel length of  $L_{\rm ch} \approx 2.1\,\mu{\rm m}$  and a gate-to-gate distance of  $L_{\rm ung} \approx 0.7\,\mu{\rm m}$ .

### Comprehensive Design-oriented FDSOI EKV Model

Hung-Chi Han, Antonio D'Amico, Christian Enz

École Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland

Email: hung.han@epfl.ch

Abstract-The work presents the comprehensive designoriented EKV model for FDSOI technologies, including the backgate effects. Despite its simplicity, the model correctly captures not only the dependency of the threshold voltage versus the back-gate, but also the changes in the slope factor and mobility. This results in a normalized transconductance efficiency that becomes independent of the back-gate voltage over a wide range. The model is validated thanks to the use of the Python-based automated parameter extraction tool on the advanced FDSOI technology.

Keywords—FDSOI,  $G_m/I_D$ , back-gate effect, inversion coefficient, low power, analog design

### EXTENDED ABSTRACT

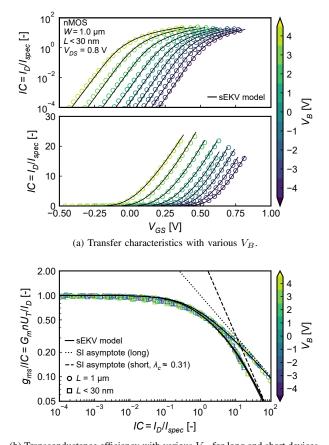

To continue the scalability of the CMOS technologies, the Fully-Depleted Silicon-On-Insulator (FDSOI) technologies overcome the short-channel effect mainly thanks to its ultrathin body. The latter, with the buried thin oxide layer, makes the FDSOI transistor an efficient four-terminal device. The so-called back-gate voltage  $(V_{back})$  allows additional freedom to the device performance. In the static mode, the threshold voltage has the significant back-gate dependency [1], and subthreshold swing and mobility [1] are slightly influenced by  $V_{back}$  due to the gates coupling and front- and back-channel formation. However, the comprehensive transconductance efficiency  $(G_m/I_D)$  considering the velocity saturation and backgate effects has not been discussed yet [2]. Therefore, the work shows the simplified EKV model adopted on a 22 nm FDSOI technology [3]. By using the open-source Pythonbased parameter extraction tool [4], the model presents the consistency of the normalized  $G_m/I_D$  over a wide  $V_B$  range.

The charge-based transfer characteristic  $I_D$ - $V_G$  in saturation is given by [5]

$$\frac{V_G - V_{T0} - nV_S}{nU_T} = 2q_s + \ln q_s$$

(1a)

$$q_s = \frac{\sqrt{4IC + (1 + \lambda_c IC)^2} - 1}{2} \qquad (1b)$$

with long-channel threshold voltage  $V_{T0}$ , source voltage  $V_S$ , thermal voltage  $U_T$ , slope factor n, inversion coefficient IC = $I_D/I_{spec}$ , specific current  $I_{spec} = I_{spec_{\Box}} W/L$  and velocity saturation parameter  $\lambda_c$ . Thanks to the log-linear inversion charge relation [6], the device bias point can be optimized within the range from weak to strong inversion. Fig. 1a shows a nice agreement between the model from (1) and transfer characteristics for a short nMOS FDSOI at different  $V_B$ . It should be noted that the parameters for the sEKV model are extracted independently from the different  $I_D$ - $V_G$  at given  $V_B$ . The significant change in the threshold voltage is well

(b) Transconductance efficiency with various  $V_B$  for long and short devices. Fig. 1. Simplified EKV model on the devices in saturation ( $V_{DS} = 0.8 \text{ V}$ ) by a 22 nm FDSOI process [3].

characterized by the extraction tool. Besides, the back-gatedependent subthreshold swing and mobility are accounted by the *n* and  $I_{spec}$ . Consequently, as shown in Fig. 1b, the normalized transconductance efficiency  $(g_{ms}/IC = G_m n U_T/I_D)$ versus IC are consistent over the  $V_B$  from -4 to 4 V for long and short devices, respectively. Despite the simplicity of the sEKV model, the  $g_{ms}/IC$  versus IC normalizes the back-gate effects and provides a reliable  $G_m/I_D$  design methodology.

- [1] H.-C. Han et al., SSE, vol. 193, p. 108296, 2022.

- [2] S. El Ghouli *et al.*, *TED*, vol. 65, no. 1, pp. 11–18, 2018.

[3] R. Carter *et al.*, in *IEDM*, 2016, pp. 2.2.1–2.2.4.

- [4] "SEKV-E," https://gitlab.com/moscm/sekv-e.

- [5] C. Enz et al., SSC-M, vol. 9, no. 3, pp. 26-35, 2017.

- [6] Y. Taur, TED, vol. 69, no. 1, pp. 427-429, 2022.

### Impact of Mechanical Bending on the Performance of Organic Thin-Film Transistors and the Characteristic Temperature of the Density of States

Aristeidis Nikolaou<sup>1,2</sup>, Jakob Leise<sup>1,2</sup>, Jakob Pruefer<sup>1,2</sup>, Ute Zschieschang<sup>3</sup>, Hagen Klauk<sup>3</sup>, Ghader Darbandy<sup>1</sup>, Benjamin Iñiguez<sup>2</sup>, Alexander Kloes<sup>1</sup>

<sup>1</sup> NanoP, TH Mittelhessen University of Applied Sciences, 35390 Giessen, Germany

<sup>2</sup> DEEEA, Universitat Rovira i Virgili, Tarragona, Spain

<sup>3</sup> Max Planck Institute for Solid State Research, Stuttgart 70569, Germany

e-mail: aristeidis.nikolaou@ei.thm.de

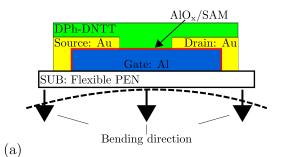

### EXTENDED ABSTRACT

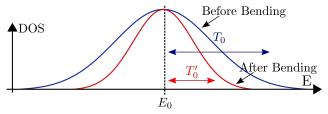

The electrical performance of organic TFTs fabricated on flexible substrates can degrade under mechanical stress that may arise from bending, twisting or stretching of the substrate. In the current paper, the effect of bending (Fig. 1) on the electrical characteristics of organic thin-film transistors is studied, using experimental data obtained from a large number of discrete organic transistors fabricated on a flexible polymeric substrates, in the coplanar device architecture. By adapting a physics-based compact model [1]-[4] to the measurement results, conclusions regarding the impact of bending on the device physics are drawn.

The transistors under bending-stress presented a significant drain-current degradation that can be mainly attributed to the respected reduction of the effective carrier mobility value. By correlating a power-law mobility model and the basics of percolation theory, the observed mobility degradation could be attributed to a decrease of the characteristic temperature that describes the shape of the Gaussian density of states in the utilized organic semiconductor (Fig. 2).

#### References

- [1] F. Hain, M. Graef, B. Iñíguez, and A. Kloes, "Charge based, continuous compact model for the channel current in organic thin-film transistors for all regions of operation," Solid-State Electronics, vol. 133, pp. 17 - 24, 2017.

- [2] J. Pruefer, J. Leise, G. Darbandy, A. Nikolaou, H. Klauk, J. W. Borchert, B. Iñíguez, T. Gneiting, and A. Kloes, "Compact modeling of shortchannel effects in staggered organic thin-film transistors," IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 5082-5090, 2020.

- [3] J. Leise, J. Pruefer, A. Nikolaou, G. Darbandy, H. Klauk, B. Iñiguez, and A. Kloes, "Macromodel for ac and transient simulations of organic thin-film transistor circuits including nonquasistatic effects," IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 4672-4676, 2020.

- A. Nikolaou, G. Darbandy, J. Leise, J. Pruefer, J. W. Borchert, M. Geiger, H. Klauk, B. Iñiguez, and A. Kloes, "Charge-based model for the draincurrent variability in organic thin-film transistors due to carrier-number and correlated- mobility fluctuation," IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 4667-4671, 2020.

This project is funded by the German Federal Ministry of Education and Research ("SOMOFLEX", No. 13FH015IX6) and the German Research Foundation (DFG) under the grant KL 1042/9-2 (SPP FFlexCom). We would like to thank AdMOS GmbH for support.

(b)

Figure 1. (a) Schematic cross-section of organic TFTs fabricated in the inverted coplanar (bottom-gate, bottom-contact) device architecture on a flexible polymeric substrate. Mechanical bending is performed in the direction perpendicular to the path of the electric current in the transistor channel. (b) Photograph of the bending experiment. The substrate is attached to the outside of a cylindrical tube with a diameter of 20 mm.

Figure 2. Narrowing of the tails of the Gaussian DOS due to the bending of the flexible substrate. The characteristic temperature  $T_0$  (prior to bending) is decreased to  $T'_0$  upon bending.

### Multidomain Modeling for Reliability Evaluation of Devices and Microsystems Using Verilog-A

Jean-Baptiste Kammerer<sup>1</sup>, Maroua Garci<sup>1</sup>, Fabien Prégaldiny<sup>1</sup>, Luc Hébrard<sup>1</sup>,

Achraf Kaïd<sup>2</sup>, Fabrice Roqueta<sup>2</sup> <sup>1</sup>ICube, Strasbourg, France <sup>2</sup>STMicroelectronics, Tours, France

### EXTENDED ABSTRACT

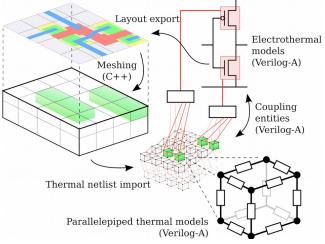

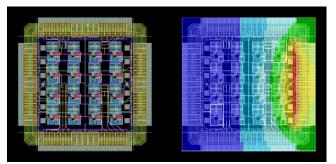

With the continuous increase in integration density induced by technology scaling and chip stacking, the dissipated power density has reached a critical level and thermal issues are now a major concern. Currently, evaluating the thermal behavior of a chip is generally done either thanks to finite element method (FEM) software coupled to a SPICE simulator or thanks to a strongly coupled electrothermal simulation in FEM software. However, these approaches are complex, time consuming and sometimes even not feasible. In addition, coupling circuit simulation and thermal FEM simulation is generally a complex task. Thereby, the need for a user-friendly tool designed to evaluate the temperature distribution inside an integrated system through standard circuit simulation arises. Analog hardware description languages such as Verilog-A offer the opportunity to manipulate thermal quantities thus allowing to perform electrothermal simulation of devices and systems in a standard microelectronics CAD environment. Taking advantage of the capabilities of these hardware description languages, a general methodology consisting in layout driven meshing and thermal modeling of the chip associated to electrothermal compact modeling of devices has been developed at ICube laboratory (Fig.1). This approach allowed us to develop a tool able to generate an electrothermal netlist of an integrated circuit suitable to SPICE-like simulators [1]. This tool which is fully integrated in the Cadence environment enables the SPICE electrothermal simulation of integrated circuits. To address large system simulations, a high-level

Fig. 1. Layout driven electrothermal netlist construction

Fig. 2. Full chip electrothermal simulation. The original layout is shown on the left while the temperature map superimposed to the same layout is shown on the right.

electrothermal modeling method has been developed [2]. It consists in simulating the functional blocks (amplifier, ADC, filter, ...) subjected to specific thermal gradients in order to determine how average temperature and temperature gradients affect their behavior. From the obtained data, one can develop accurate behavioral models of the functional blocks of a large integrated system, allowing to perform fast full-chip electrothermal simulations (Fig.2). Recently, our tool has been adapted to power electronics industry for discrete device simulation [3]. Finally, the possibility of implementing other physical effects has been demonstrated. In particular, the thermal induced mechanical stress has been successfully simulated. This approach leads to a powerful and versatile tool able to address reliability issues such as overheating, hot spot detection, thermal drift of the performances or even thermal induced delamination [4].

- J-C. Krencker, J-B. Kammerer, Y. Hervé, L. Hébrard, "3D electrothermal simulations of analog ICs carried out with standard CAD tools and Verilog-A," 17th International Workshop on Thermal investigations of ICs and Systems (THERMINIC 2011), 2011

- [2] J-C. Krencker, J-B. Kammerer, Y. Hervé, L. Hébrard, "Electro-thermal high-level modeling of integrated circuits," Microelectronics Journal, Volume 45, Number 5, page 491-499, 2014

- [3] A. Kaïd, J-B. Kammerer, F. Roqueta, L. Hébrard, "Novel method for modelling the local electro-thermal behaviour of discrete power diode using Verilog-A in a standard CAD environment," 23rd International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EUROSIME 2022), 2022

- [4] M. Garci, J-B. Kammerer, L. Hébrard, "Direct Electro-Thermo-Mechanical Simulation of Integrated Circuits with Spectre," CDN Live EMEA, Munich, Germany, Cadence (Eds.), 2016

### Optimization-based Determination of TFT contact Resistances in Python

M. Helena Fino

Department of Electrotechnical and Computer Engineering Nova School of Science and Technology Caparica, Portugal hfino@fct.unl.pt

Abstract—The paper presents an optimization-based methodology for the determination of thin-film transistors contact resistances. The implementation of the proposed methodology in Python is presented. The validity of results obtained against devices characteristics is demonstrated. The advantage and limitations of the proposed methodology is also discussed.

#### *Keywords*—TFTs, compact model, contact resistances

#### I. INTRODUCTION

Due to the wide spread use of thin-film transistors (TFT) in a wide range of applications e.g., displays, radio-frequency identification tags (RIFID), or flexible electronics [1] a strong effort has been paid to the development of TFT compact models, [2]. In [3] a model-oriented methodology for the determination of TFT parameters and its automatic implementation in Python is presented. This paper considers an extension of this previous methodology, where the TFT contact resistances are also evaluated.

### II. THIN FILM TRANSISTOR MODEL

Although the transport characteristics of TFTs are very different for the different active materials, the current-voltage characteristic of these was initially evaluated using the Mosfets Schokley model. In [4] a more accurate expression is proposed for TFT in saturation, and is given by:

$$I_D = \frac{W}{L_{eff}} \cdot \frac{\mu_0}{V_{AA}{}^{\gamma}} C_{ox} \alpha_s, \left(V_{gs} - V_t\right)^{2+\gamma}, \tag{1}$$

where  $\mu_0$  is the carrier mobility at low bias,  $\gamma$  is the mobility enhancement factor,  $V_{AA}$  is a fitting parameter and  $\alpha_s$  is also a fitting parameter that relates the saturation voltage overdrive. Should the contact resistances be considered, then the analytical expression for the drain current should reflect its dependence on the intrinsic voltages between the gate and source,  $V_{gs}$  and between the drain and the source,  $V_{ds}$ . These intrinsic voltages may be obtained with

$$V_{gs} = V_{GS} - I_D R_s \tag{3.a}$$

$$V_{ds} = V_{DS} - I_D (R_D + R_S)$$

(3.b)

where  $V_{GS}$  and  $V_{DS}$  are the externally applied voltages between gate and source and between drain and source respectively. By combining 3.a) with (1) an implicit function for the drain current evaluation is obtained

$$I_{D} = K(V_{GS} - I_{D}R_{S} - V_{t})^{m},$$

(4)

In this paper, two methodologies for the automatic evaluation of TFT parameters are implemented in Python and results obtained are compared. In the first case the methodology proposed in [3] is applied for the determination of the TFT parameters, where the contact resistances are neglected. Then, the solution obtained is considered as an initial point for the automatic determination of the gate resistance. In the second case the methodology proposed in [4] is implemented.

- Y. He, X. Wang, Y. Gao, Y. Hou, and Q. Wan, "Oxide-based thin film transistors for flexible electronics," *J. Semicond.*, vol. 39, no. 1, 2018, doi: 10.1088/1674-4926/39/1/011005.

- [2] N. Lu, W. Jiang, Q. Wu, D. Geng, L. Li, and M. Liu, "A review for compact model of thin-film transistors (TFTs)," *Micromachines*, vol. 9, no. 11, 2018, doi: 10.3390/mi9110599.

- [3] M. H. Fino and P. Barquinha, "A Model-oriented Methodology for the Automatic Parameter Extraction of TFT Model. BT - 2021 28th International Conference on Mixed Design of Integrated Circuits and System, Lodz, Poland, June 24-26, 2021." pp. 27–30, 2021, doi: 10.23919/MIXDES52406.2021.9497605.

- [4] R. Rodriguez-Davila, A. Ortiz-Conde, C. Avila-Avendano, and M. A. Quevedo-Lopez, "A New Integration-Based Procedure to Extract the Threshold Voltage, the Mobility Enhancement Factor, and the Series Resistance of Thin-Film MOSFETs," *IEEE Trans. Electron Devices*, vol. 66, no. 7, pp. 2979–2985, 2019, doi: 10.1109/TED.2019.2913699.

This work is funded in part by the Portuguese "Fundação para a Ciência e a Tecnologia" (FCT) in the context of the Center of Technology and Systems CTS/UNINOVA/FCT/NOVA, reference UIDB/00066/2020"

# Design of Integrated Circuits and Microsystems

### 8-bit Low-Power, Low-Area SAR ADC for Biomedical Multichannel Integrated Recording System in CMOS 40nm

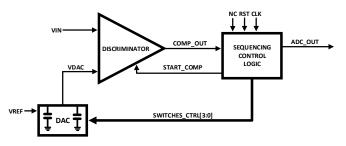

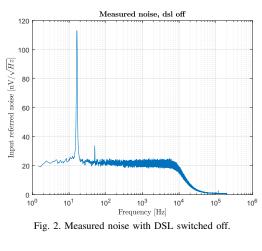

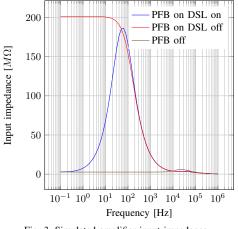

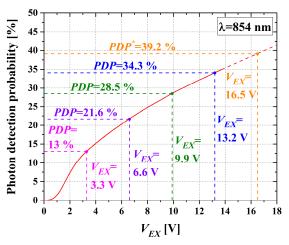

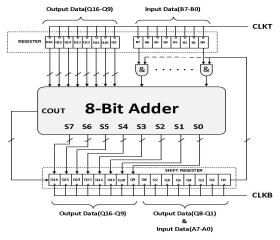

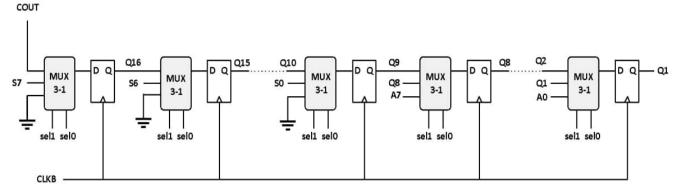

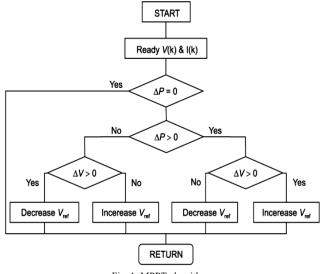

Magdalena Rosół, Piotr Kmon Department of Measurement and Electronics AGH University of Science and Technology Krakow, Poland magdalena@student.agh.edu.pl, kmon@agh.edu.pl